# Universal Programmable Clock Generator (UPCG)

#### **Features**

■ Integrated phase-locked loop (PLL)

■ Field programmable

■ Input frequency range:

□ Crystal: 8–30 MHz

□ CLKIN: 1–133 MHz

■ Output frequency:

□ LVCMOS: 1–200 MHz

■ Low jitter, high accuracy outputs

■ 3.3V operation

■ 8-pin SOIC package

## **Benefits**

- Inventory of only one device, CY22801, is needed to use in various applications

- In-house programming of samples and prototype quantities is available using the CY36800 InstaClock Kit

- Can customize the input and output frequencies to suit your needs

- High-performance PLL tailored for multiple applications

- Meets critical timing requirements in complex system designs

- Enables application compatibility

## **Pin Configuration**

Figure 1. CY22801 8-Pin SOIC

Table 1. Pin Definition

| Name | Pin Number | Description                                                                                                                                    |

|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| XIN  | 1          | Reference Input: Crystal or External Clock                                                                                                     |

| VDD  | 2          | 3.3V Voltage Supply                                                                                                                            |

| NC   | 3          | No Connect; leave this pin floating                                                                                                            |

| VSS  | 4          | Ground                                                                                                                                         |

| CLKB | 5          | Clock Output B                                                                                                                                 |

| CLKA | 6          | Clock Output A                                                                                                                                 |

| CLKC | 7          | Clock Output C                                                                                                                                 |

| XOUT | 8          | Reference Output: Connect to external crystal. When the reference is an external clock signal, this pin is not used and must be left floating. |

## General Description

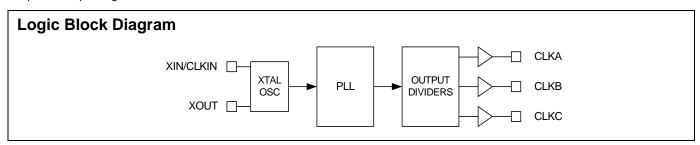

The CY22801 is a flash-programmable clock generator that supports various applications in consumer and communications markets. The device uses a Cypress proprietary PLL to drive up to three configurable outputs in an 8-pin SOIC.

The CY22801 can be programmed with an easy-to-use programmer dongle, the CY36800, in conjunction with the CyClocksRT™ software. This enables fast sample generation of prototype builds for user-defined frequencies.

## Field Programming the CY22801

The CY22801 is programmed using the CY36800 USB programmer dongle. The CY22801 is flash-technology based, so the parts can be reprogrammed up to 100 times. This enables fast and easy design changes and product updates, and eliminates any issues with old and out-of-date inventory.

Samples and small prototype quantities can be programmed using the CY36800 programmer. Cypress's value added distribution partners and third party programming systems from BP Microsystems, HiLo Systems, and others, are available for large production quantities.

## CyClocksRT Software

CyClocksRT is an easy-to-use software application that enables the user to custom-configure the CY22801. Users can specify the XIN/CLKIN frequency, crystal load capacitance, and output frequencies. CyClocksRT then creates an industry-standard JEDEC file, which is used to program the CY22801.

When needed, an advanced mode is available that enables users to override the automatically generated VCO frequency and output divider values.

CyClocksRT is a component of the CyberClocks<sup>™</sup> software, which can be downloaded free of charge from the Cypress website at http://www.cypress.com.

#### CY36800 InstaClock™ Kit

The Cypress CY36800 InstaClock Kit comes with everything needed to design the CY22801 and program samples and small prototype quantities. The CyClocksRT software is used to quickly create a JEDEC programming file, which is then downloaded directly to the portable programmer that is included in the CY36800 InstaClock Kit. The JEDEC file can also be saved for use in a production programming system for larger volumes.

The CY36800 also comes with five samples of the CY22800, which can be programmed with preconfigured JEDEC files using the InstaClock software.

## **Output Clock Frequencies**

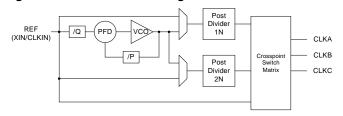

The CY22801 is a very flexible clock generator with up to three individual outputs, generated from an integrated PLL. Details are shown in Figure 2.

The output of the PLL runs at high frequency and is divided down to generate the output clocks. Two programmable dividers are available for this purpose. Thus, although the output clocks may be different frequencies, they must be related, based on the PLL frequency.

It is also possible to direct the reference clock input to any of the outputs, thereby bypassing the PLL. Lastly, the reference clock may be passed through either divider.

Figure 2. Basic PLL Block Diagram

## **Reference Crystal Input**

The input crystal oscillator of the CY22801 is an important feature because of the flexibility it allows the user in selecting a crystal as a reference clock source. The oscillator inverter has programmable gain, enabling maximum compatibility with a reference crystal, based on manufacturer, process, performance, and quality.

Input load capacitors are placed on the CY22801 die to reduce external component cost. These capacitors are true parallel-plate capacitors, designed to reduce the frequency shift that occurs when nonlinear load capacitance is affected by load, bias, supply, and temperature changes.

The value of the input load capacitors is determined by eight bits in a programmable register. Total load capacitance is determined by the formula:

$$CapLoad = (C_L - C_{BRD} - C_{CHIP})/0.09375 \text{ pF}$$

In CyClocksRT, enter the crystal capacitance ( $C_L$ ). The value of CapLoad will be determined automatically and programmed into the CY22801.

## **Applications**

#### **Controlling Jitter**

Jitter is defined in many ways, including:

- Phase noise

- Long-term jitter

- Cycle-to-cycle jitter

- Period jitter

- Absolute jitter

- Deterministic jitter

These jitter terms are usually given in terms of RMS, peak-to-peak, or in the case of phase noise, dBC/Hz with respect to the fundamental frequency. Actual jitter is dependent on

- XIN jitter and edge rate

- Number of active outputs

- Output frequencies

- Supply voltage

- Temperature

- Output load

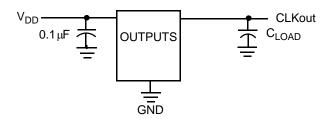

Power supply noise and clock output loading are two major system sources of clock jitter. Power supply noise can be mitigated by proper power supply decoupling (0.1-µF ceramic cap) of the clock and ensuring a low impedance ground to the

chip. Reducing capacitive clock output loading to a minimum lowers current spikes on the clock edges and thus reduces jitter.

Reducing the total number of active outputs also reduces jitter in a linear fashion. However, it is better to use two outputs to drive two loads than one output to drive two loads.

For additional information, refer to the application note, *Jitter in PLL-based Systems: Causes, Effects, and Solutions*, available at <a href="http://www.cypress.com">http://www.cypress.com</a>.

## **Cypress Programmable Clocks**

Cypress offers a wide range of programmable clock synthesizers that can generate any other frequencies not covered by the CY22801. Table 2 summarizes all Cypress programmable devices including CY22801.

Table 2. Cypress Programmable Clocks<sup>[1]</sup>

| Part #        | No. of PLL | Input Freq. | Output<br>Freq. | Package                | No. of<br>Outputs | Spread<br>Spectrum | vсхо | I <sup>2</sup> C |

|---------------|------------|-------------|-----------------|------------------------|-------------------|--------------------|------|------------------|

| CY22800       | 1          | 0.5–100     | 1–200           | 8-SOIC                 | up to 3           | Yes                | Yes  | No               |

| CY22801       | 1          | 1–133       | 1–200           | 8-SOIC                 | up to 3           | No                 | No   | No               |

| CY22050       | 1          | 1–133       | 0.08-200        | 16-TSSOP               | up to 6           | No                 | No   | No               |

| CY22150       | 1          | 1–133       | 0.08-200        | 16-TSSOP               | up to 6           | No                 | No   | Yes              |

| CY25100       | 1          | 8–166       | 3–200           | 8-SOIC/TSSOP           | up to 2           | Yes                | No   | No               |

| CY25200       | 1          | 3–166       | 3–200           | 16-TSSOP               | up to 6           | Yes                | No   | No               |

| CY241V08      | 1          | 27/13.5     | 27/13.5         | 8-SOIC                 | up to 2           | No                 | Yes  | No               |

| CY22392       | 3          | 1–166       | 1–200           | 16-TSSOP               | up to 6           | No                 | No   | No               |

| CY22381       | 3          | 1–166       | 1–200           | 8-SOIC                 | up to 3           | No                 | No   | No               |

| CY22393       | 3          | 1–166       | 1–200           | 16-TSSOP               | up to 6           | No                 | No   | Yes              |

| CY22394/5     | 3          | 1–166       | 1–200           | 16-TSSOP               | up to 5           | No                 | No   | No               |

| CY22388/89/91 | 4          | 1–100       | 4.2–166         | 16/20-TSSOP,<br>32-QFN | up to 8           | No                 | Yes  | No               |

#### Note

<sup>1.</sup> The CY22800 and CY22801 are programmed using the programming dongle included in the CY36800 InstaClock Kit. The CY3672 programmer can be used to program all other Cypress Programmable Clocks.

## **Absolute Maximum Conditions**

| Parameter       | Description                                                   | Min             | Max                   | Unit |

|-----------------|---------------------------------------------------------------|-----------------|-----------------------|------|

| $V_{DD}$        | Supply Voltage                                                | -0.5            | 4.6                   | V    |

| $T_S$           | Storage Temperature                                           | <del>-</del> 65 | 150                   | °C   |

| $T_J$           | Junction Temperature                                          | _               | 125                   | °C   |

| V <sub>IO</sub> | Input and Output Voltage                                      | $V_{SS} - 0.5$  | V <sub>DD</sub> + 0.5 | V    |

| ESD             | Electro-Static Discharge Voltage per MIL-STD-833, Method 3015 | 2000            | ı                     | V    |

## **Recommended Operating Conditions**

| Parameter         | Description                                                                              | Min  | Тур | Max  | Unit |

|-------------------|------------------------------------------------------------------------------------------|------|-----|------|------|

| $V_{DD}$          | Operating Voltage                                                                        | 3.14 | 3.3 | 3.47 | V    |

| T <sub>A</sub>    | Ambient Temperature                                                                      | 0    | _   | 70   | °C   |

| C <sub>LOAD</sub> | Max. Load Capacitance on the CLK output                                                  | _    | _   | 15   | pF   |

| t <sub>PU</sub>   | Power up time for VDD to reach minimum specified voltage (power ramps must be monotonic) | 0.05 | -   | 500  | ms   |

# **Recommended Crystal Specifications**

| Parameter         | Name                               | Description                                      | Min | Тур | Max | Unit |

|-------------------|------------------------------------|--------------------------------------------------|-----|-----|-----|------|

| F <sub>NOM</sub>  |                                    | Parallel resonance, fundamental mode, and AT cut | 8   | -   | 30  | MHz  |

| C <sub>LNOM</sub> | Nominal Load Capacitance           |                                                  | 6   | _   | 30  | pF   |

| R <sub>1</sub>    | Equivalent Series Resistance (ESR) | Fundamental mode                                 | _   | 35  | 50  | Ω    |

| DL                | Crystal Drive Level                | No external series resistor assumed              | _   | 0.5 | 2   | mW   |

# DC Electrical Specifications<sup>[2]</sup>

| Parameter                         | Name                           | Description                                        | Min                   | Тур | Max                   | Unit |

|-----------------------------------|--------------------------------|----------------------------------------------------|-----------------------|-----|-----------------------|------|

| I <sub>OH</sub>                   | Output High Current            | $V_{OH} = V_{DD} - 0.5$ , $V_{DD} = 3.3V$ (source) | 12                    | 24  | -                     | mA   |

| I <sub>OL</sub>                   | Output Low Current             | $V_{OL} = 0.5, V_{DD} = 3.3V \text{ (sink)}$       | 12                    | 24  | _                     | mA   |

| V <sub>IH</sub>                   | Input High Voltage             |                                                    | 0.7*V <sub>DD</sub>   | -   | V <sub>DD</sub> + 0.3 | V    |

| V <sub>IL</sub>                   | Input Low Voltage              |                                                    | V <sub>SS</sub> - 0.3 | -   | 0.3*V <sub>DD</sub>   | V    |

| C <sub>IN1</sub>                  | Input Capacitance              | All input pins except XIN and XOUT                 | _                     | -   | 7                     | pF   |

| C <sub>IN2</sub>                  | Input Capacitance              | XIN and XOUT pins                                  | _                     | 24  | -                     | pF   |

| I <sub>DD</sub> <sup>[3, 4]</sup> | V <sub>DD</sub> Supply Current |                                                    | _                     | 70  | _                     | mA   |

#### Notes

- Not 100% tested, guaranteed by design.

IpD current specified for three CLK outputs running at 100 MHz.

Use CyClocksRT™ to calculate actual IDD for specific output frequency configurations.

## AC Electrical Characteristics<sup>[2]</sup>

| Parameter                     | Name                          | Description                                               | Min | Тур | Max | Unit |

|-------------------------------|-------------------------------|-----------------------------------------------------------|-----|-----|-----|------|

| f <sub>REFC</sub>             | Reference Frequency - crystal |                                                           | 8   | _   | 30  | MHz  |

| f <sub>REFD</sub>             | Reference Frequency - driven  |                                                           | 1   | _   | 133 | MHz  |

| f <sub>OUT</sub>              | Output Frequency              |                                                           | 1   | -   | 200 | MHz  |

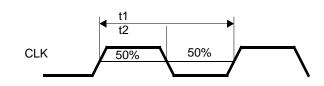

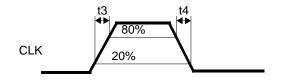

| DC                            | Output Duty Cycle             | Duty Cycle is defined in Figure 4, 50% of V <sub>DD</sub> | 45  | 50  | 55  | %    |

| t <sub>3</sub>                | Rising Edge Slew Rate         | Output Clock Rise Time, 20% - 80% of V <sub>DD</sub>      | 0.8 | 1.4 | _   | V/ns |

| t <sub>4</sub>                | Falling Edge Slew Rate        | Output Clock Fall Time, 80% - 20% of V <sub>DD</sub>      | 0.8 | 1.4 | _   | V/ns |

| t <sub>5</sub> <sup>[5]</sup> | Skew                          | Output-output skew between related outputs                | _   | _   | 250 | ps   |

| t <sub>6</sub> <sup>[6]</sup> | Clock Jitter                  | Peak-to-peak period jitter                                | _   | 250 | _   | ps   |

| t <sub>10</sub>               | PLL Lock Time                 |                                                           | _   | _   | 3   | ms   |

## **Test Circuit**

## Figure 3. Test Circuit Diagram

# **Timing Definitions**

Figure 4. Duty Cycle Definition; DC = t2/t1

Figure 5. Rise and Fall Time Definitions

#### Notes

- 5. Skew value guaranteed when outputs are generated from the same divider bank.

- 6. Jitter measurement may vary. Actual jitter is dependent on input jitter and edge rate, number of active outputs, input and output frequencies, supply voltage, temperature, and output load. For more information, refer to the application note, *Jitter in PLL-based Systems: Causes, Effects, and Solutions*.

# **Ordering Information**

| Ordering Code                     | Package Type             | Operating Range | Operating Voltage |

|-----------------------------------|--------------------------|-----------------|-------------------|

| CY22801FXC <sup>[7]</sup>         | 8-Pin SOIC               | Commercial      | 3.3V              |

| CY22801FXCT <sup>[7]</sup>        | 8-Pin SOIC-Tape and Reel | Commercial      | 3.3V              |

| CY22801FXI <sup>[7]</sup>         | 8-Pin SOIC               | Industrial      | 3.3V              |

| CY22801FXIT <sup>[7]</sup>        | 8-Pin SOIC-Tape and Reel | Industrial      | 3.3V              |

| CY22801SXC-xxx <sup>[7, 8]</sup>  | 8-Pin SOIC               | Commercial      | 3.3V              |

| CY22801SXC-xxxT <sup>[7, 8]</sup> | 8-Pin SOIC-Tape and Reel | Commercial      | 3.3V              |

| CY22801KFXC                       | 8-Pin SOIC               | Commercial      | 3.3V              |

| CY22801KFXCT                      | 8-Pin SOIC-Tape and Reel | Commercial      | 3.3V              |

| CY22801KFXI                       | 8-Pin SOIC               | Industrial      | 3.3V              |

| CY22801KFXIT                      | 8-Pin SOIC-Tape and Reel | Industrial      | 3.3V              |

| CY22801KSXC-xxx <sup>[8]</sup>    | 8-Pin SOIC               | Commercial      | 3.3V              |

| CY22801KSXC-xxxT <sup>[8]</sup>   | 8-Pin SOIC-Tape and Reel | Commercial      | 3.3V              |

## **Package Diagram**

Figure 6. 8-Lead (150-Mil) SOIC S8 1. DIMENSIONS IN INCHES[MM] MIN. MAX. 2. PIN 1 ID IS OPTIONAL, ROUND ON SINGLE LEADFRAME 0.150[3.810] RECTANGULAR ON MATRIX LEADFRAME 0.157[3.987] 3. REFERENCE JEDEC MS-012 0.230[5.842] 4. PACKAGE WEIGHT 0.07gms 0.244[6.197] PART # S08.15 STANDARD PKG. SZ08.15 LEAD FREE PKG. 0.189[4.800] 0.010[0.254] SEATING PLANE 0.016[0.406] 0.061[1.549] 0.068[1.727] 0.050[1.270] 0.0075[0.190] 0.004[0.102] 0.016[0.406] 0.0098[0.249]

## Notes

0.0138[0.350] 0.0192[0.487]

51-85066-\*C

Not recommended for new designs.

Ordering codes with "xxx" are factory-programmed configurations. Factory programming is available for high-volume orders. For more details, contact your local Cypress field application engineer or Cypress sales representative.

## **Document History Page**

|      | Document Title: CY22801 Universal Programmable Clock Generator (UPCG)<br>Document Number: 001-15571 |                    |                    |                                                                                                                                                                                                                                                                                              |  |  |  |

|------|-----------------------------------------------------------------------------------------------------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| REV. | ECN NO.                                                                                             | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                        |  |  |  |

| **   | 1058080                                                                                             | KVM/<br>KKVTMP     | 05/10/07           | New data sheet                                                                                                                                                                                                                                                                               |  |  |  |

| *A   | 2440787                                                                                             | AESA               | 05/16/08           | Updated template. Added Note 7 and 8. Added existing part numbers CY22801FXCT, CY22801FXI, CY22801FXIT, CY22801SXC-xxx and CY22801SXC-xxxT in ordering information table. Added new part numbers CY22801KFXC, CY22801KFXCT, CY22801KFXI, CY22801KFXIT, CY22801KSXC-xxx and CY22801KSXC-xxxT. |  |  |  |

## Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at cypress.com/sales.

| Products         |                      | PSoC Solutions        |                                   |

|------------------|----------------------|-----------------------|-----------------------------------|

| PSoC             | psoc.cypress.com     | General               | psoc.cypress.com/solutions        |

| Clocks & Buffers | clocks.cypress.com   | Low Power/Low Voltage | psoc.cypress.com/low-power        |

| Wireless         | wireless.cypress.com | Precision Analog      | psoc.cypress.com/precision-analog |

| Memories         | memory.cypress.com   | LCD Drive             | psoc.cypress.com/lcd-drive        |

| Image Sensors    | image.cypress.com    | CAN 2.0b              | psoc.cypress.com/can              |

|                  |                      | USB                   | psoc.cypress.com/usb              |

© Cypress Semiconductor Corporation, 2007-2008. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document #: 001-15571 Rev. \*A

Revised May 16, 2008

Page 7 of 7